IT в России и мире в реалиях мирового кризиса

1,286,471

7,816

|

|

mrt789 ( Слушатель ) |

| 23 авг 2020 02:13:54 |

Эльбрус в чьих-то руках

новая дискуссия Дискуссия 240

https://www.youtube.…uWzWtXHimk

Дум3 показывают, процессор там нужен чисто чтобы был - он на 20% загружен.

Ну и там в комментах циферки сравнивают:

>По тесту 7z это получается примерно аналог i5 750. А по тесту памяти примерно i7 920, а второй тест показал значения i7 2600 похоже. Тест где была эмуляция x86 в wine было 166793, а i7 2500k набрал 224181, Близкий по результатам AMD Phenom II X4 905e @ 2.50 GHZ. Но все это попугаи и этому не стоит верить.

>судя по бенчам...результат вообще неплохой....уровня i3 6100 или atlon 200GE....а на этих процессорах можно играть практически во всё....да и частота этих процессоров выше 3.5ггц...ну и то что они 2х ядерные \ 4х поточные!!!! уровень неплохой.....правда цена их в районе 50$....можно даже сказать что эльбрус тащит!!!

Мой коммент по нерешаемым проблемам влива на задачах "общего назначения" и невозможность предсказывать переходы на этапе компиляции остается в силе.

Дум3 показывают, процессор там нужен чисто чтобы был - он на 20% загружен.

Ну и там в комментах циферки сравнивают:

>По тесту 7z это получается примерно аналог i5 750. А по тесту памяти примерно i7 920, а второй тест показал значения i7 2600 похоже. Тест где была эмуляция x86 в wine было 166793, а i7 2500k набрал 224181, Близкий по результатам AMD Phenom II X4 905e @ 2.50 GHZ. Но все это попугаи и этому не стоит верить.

>судя по бенчам...результат вообще неплохой....уровня i3 6100 или atlon 200GE....а на этих процессорах можно играть практически во всё....да и частота этих процессоров выше 3.5ггц...ну и то что они 2х ядерные \ 4х поточные!!!! уровень неплохой.....правда цена их в районе 50$....можно даже сказать что эльбрус тащит!!!

Мой коммент по нерешаемым проблемам влива на задачах "общего назначения" и невозможность предсказывать переходы на этапе компиляции остается в силе.

ОТВЕТЫ (13)

|

|

Longspig ( Слушатель ) |

| 23 авг 2020 22:33:21 |

Цитата: mrt789 от 23.08.2020 02:13:54

Вы меня заинтриговали. Всегда об этом мечтал! А где такое реализовано? Неужели в Интеле x64?

|

|

adolfus ( Слушатель ) |

| 04 сен 2020 03:40:59 |

Цитата: Longspig от 23.08.2020 22:33:21

На этапе компиялции нет, но на этапе исполнения управлять предсказаниями можно. Префиксы есть, с помощью которых можно указать более и/или менее вероятную ветвь. Правда, исходный код нужно на ассемблере писать.

|

|

Поверонов ( Слушатель ) |

| 04 сен 2020 07:22:03 |

Цитата: adolfus от 04.09.2020 03:40:59

Какая разница на этапе исполнения на чем написан исходный код ? - исполняется машинный код

|

|

Senya ( Слушатель ) |

| 04 сен 2020 08:26:52 |

Цитата: Поверонов от 04.09.2020 07:22:03

Тут я давно отстал от темы, но кто мешает предвычислить несколько ветвей одновременно? Теневые наборы регистров давно вроде появились, вопрос только в свободном вычислительном блоке.

|

|

Поверонов ( Слушатель ) |

| 05 сен 2020 16:49:08 |

Цитата: Senya от 04.09.2020 08:26:52

Насколько слышал там ничего и не нужно предвычислять - цепочка команд цикла сама оседает в кэше процессора а если не оседает то и не ускоряется. Поэтому рекомендуется тяжелые циклы представлять инлайн-инклудами а не вызовами, и потому в частности интерпретататоры проигрывают компиляторам, так как в интерпретаторах циклы оказываются разнесены по подпрограммам, которые плохо оседают в кэше.

|

|

adolfus ( Слушатель ) |

| 04 сен 2020 11:51:12 |

Цитата: Поверонов от 04.09.2020 07:22:03

Разница в том, что получить нужный Вам машинный код, содеражщий префиксы управления вероятностью ветвления, кроме как использовать для этого асемблер, вы не можете. Как впрочем и задействовать кучу весьма важных инструкций x86_64. Арифметические и циклические сдвиги, например, или условную пересылку данных. Даже такую банальность, как арифметические расширения SIMD из ЯВУ можно задействовать, только указав компилятору использовать их или не использовать целиком для всего модуля через опции компиляции.

|

|

Longspig ( Слушатель ) |

| 04 сен 2020 16:41:31 |

Цитата: adolfus от 04.09.2020 03:40:59

Странно. Пошарил по описанию Jump if Condition Is Met из мануала 64-ia-32-architectures-software-developer-instruction-set-reference-manual-325383

Ничего похожего не нашел, в префиксах тоже.

Может другое подразумевалось - вариантность выбора условия перехода, т.е. ставить условие такое, где вероятность выполнения перехода меньше (если исходить из предвыборки по главной последовательности выполнения). Но это префиксов не требует, но работает не во всех случаях.

|

|

adolfus ( Слушатель ) |

| 07 сен 2020 04:07:08 |

Цитата: Longspig от 04.09.2020 16:41:31

Intel® 64 and IA-32 Architectures Software Developer’s Manual. Combined Volumes: 1, 2A, 2B, 2C, 3A, 3B and 3C, Order Number: 325462-071US. October 2019, 5038 p.

На стр. 277

11.4.5 Branch Hints

SSE2 extensions designate two instruction prefixes (2EH and 3EH) to provide branch hints to the processor (see“Instruction Prefixes” in Chapter 2 of the Intel® 64 and IA-32 Architectures Software Developer’s Manual, Volume 2A). These prefixes can only be used with the Jcc instruction and only at the machine code level (that is, there are no mnemonics for the branch hints).

на стр. 526

Branch hint prefixes (2EH, 3EH) allow a program to give a hint to the processor about the most likely code path for a branch. Use these prefixes only with conditional branch instructions (Jcc). Other use of branch hint prefixes and/or other undefined opcodes with Intel 64 or IA-32 instructions is reserved; such use may cause unpredictable behavior.

|

|

Longspig ( Слушатель ) |

| 07 сен 2020 11:00:58 |

Цитата: adolfus от 07.09.2020 04:07:08

Спасибо!

Удивлен. Обычно Intel более тщательно подходила к перекрестным ссылкам в документации и неупоминание префиксов в описании команд jcc выглядит странно. Тем более, что нынешняя "каша" множественых условий и ограничений применения добавляемых команд, делает 64-х битное программирование на асм-е занятием действительно непростым.

Млин, Intel даже согласованую мнемонику для них не создали. Формально префиксы "прихватили" из штатных префиксов команд работы с памятью - переопределения сегмента CS и DS. Теперь в NASM мне предлагают писать конструкцию типа

cs jbe Mxxx

Бр-ррр...

|

|

adolfus ( Слушатель ) |

| 08 сен 2020 02:47:00 |

Цитата: Longspig от 07.09.2020 11:00:58

Можно в секции .text написать прямо db 3EH или db 2EH перед Jxx. Или макрос сочинить.

Отладчиком для ассемблера каким пользуетесь?

|

|

Longspig ( Слушатель ) |

| 08 сен 2020 11:58:10 |

Цитата: adolfus от 08.09.2020 02:47:00

Можно, конечно. Но отсуствие штатной мнемоники удивляет (в тот же NASM ее с легкостью бы встроили, чтоб не извращаться). NASM по сути единственый, кто отслеживает новые наборы команд. Но отличия от семантики привычного TASM напрягает.

По 64-бита писать пока не пробовал т.к. не смог подобрать привычную для себя среду - монополизации всех ресурсов компа.

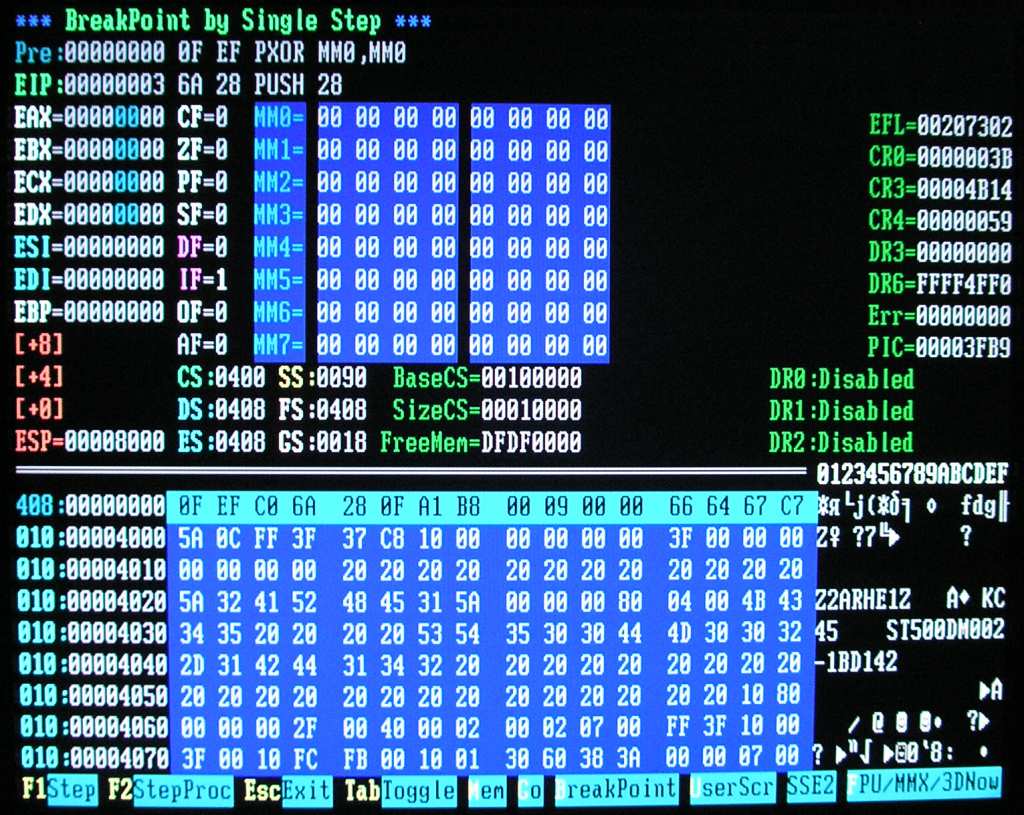

Под 32-бита, уже писал - среда своя, отладчик свой, встроеный в систему. Стиль старого доброго AFD всяк узнает!

Вроде в 32-битном режиме этот механизм тоже должен работать. Будет время - попробую. По TSC замерить скорость работы ветвей переходов не проблема (у меня же полный монополизм задачи, так что TSC абсолютно точен).

.

ПыСы: Проверил. В 32-х битном коде разницы нет "от слова совсем". На префиксы не ругается, но никак и не реагирует (с точностью до такта). И вообще. Как оказалось - пора мне, старому склерознику, "на свалку истории". У меня самопальная мнемоника этих префиксов обнаружилась встроеной в отладчик. Т.е. наткнулся таки я, когда-то, на них (за 14 лет, хрен упомнишь) и даже прописал в декодер. Но, начисто забыл и продолжаю людям "мозги клевать".

Дико извиняюсь перед участниками обсуждения.

|

|

adolfus ( Слушатель ) |

| 13 сен 2020 03:03:28 |

Цитата: Longspig от 08.09.2020 11:58:10

У nasm настолько мощный препроцессор, что любую мнемонику можно нарисовать. Он превращает ассемблер в целый класс императивных языков.

|

|

kerosene ( Слушатель ) |

| 24 авг 2020 18:21:02 |

Цитата: mrt789 от 23.08.2020 02:13:54

Я там видел только какого-то Sheti Ashcrof, который транслировал в комментариях набор бредовых "фактов" про мнимые недостатки VLIW.